risc-v指令架构基础

RISC-V指令基础

RV32

RV32I

RV32M

RV32F & RV32D

RV32A

RV32C

RV32V

RV64

RV64I

RV64M & RV64A

RV64F & RV64D

RV64C

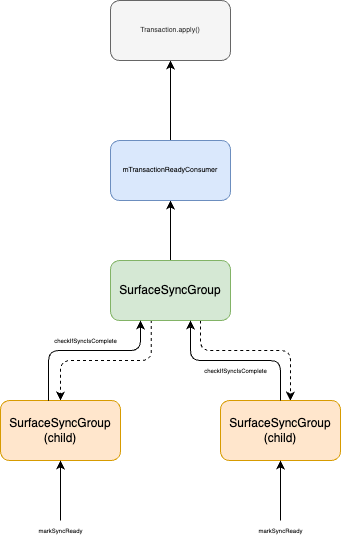

RiscV中断

分类

在Riscv中中断的类型分为3种

software interrupt——软件中断

timer interrupt——时钟中断

external interrupt——外部中断

mstatus(Machine Status),维护各种状态,如全局中断使能状态。

mip(Machine Interrupt Pending),记录当前的中断请求。

mie(Machine Interrupt Enable),维护处理器的中断使能状态。

mcause(Machine Exception Cause),指示发生了何种异常。

mtvec(Machine Trap Vector),存放发生异常时处理器跳转的地址。

mtval(Machine Trap Value),存放与当前自陷相关的额外信息,如地址异常的故障地址、非法指令异常的指令,发生其他异常时其值为0。

mepc(Machine Exception PC),指向发生异常的指令。

mscratch(Machine Scratch),向异常处理程序提供一个字的临时存储。

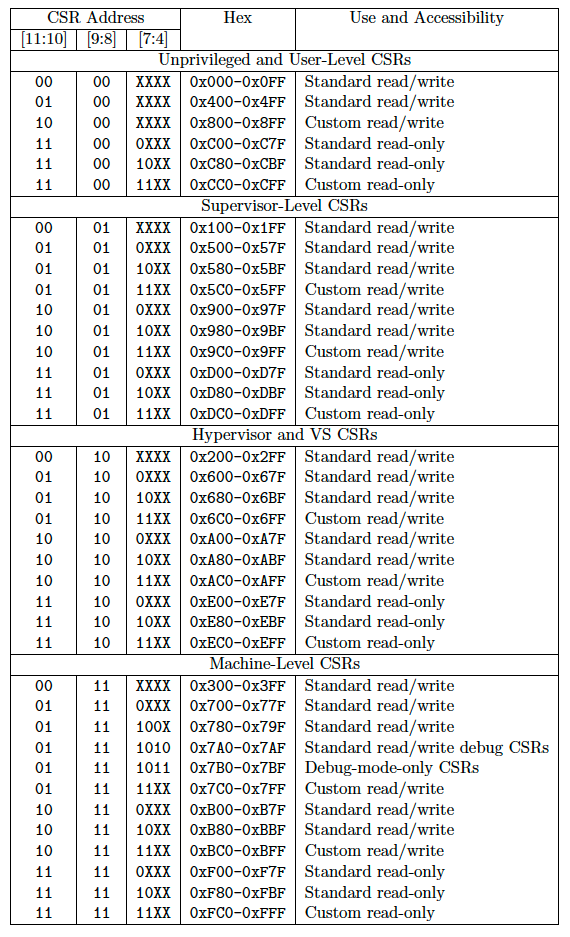

RiscV特权

在RiscV中有3大权限模式

M——Machine Mode

最简单嵌入式系统只支持Machine模式

S——Supervisor Mode

支持虚拟内存概念的类Unix系统,需要支持Machine,User和Supervisor三种模式

U——User Mode

安全的嵌入式系统支持Machine模式和User模式

特权指令

- sret : 监管者模式下的异常和中断返回

- mret : 机器模式下的异常和中断返回

- sfence.vma : 刷新虚拟内存映射(tlb)

- wfi :使处理器暂停执行,并进入低功耗的等待状态,使处理器暂停执行,并进入低功耗的等待状态

特权级切换

1 | .section .text |

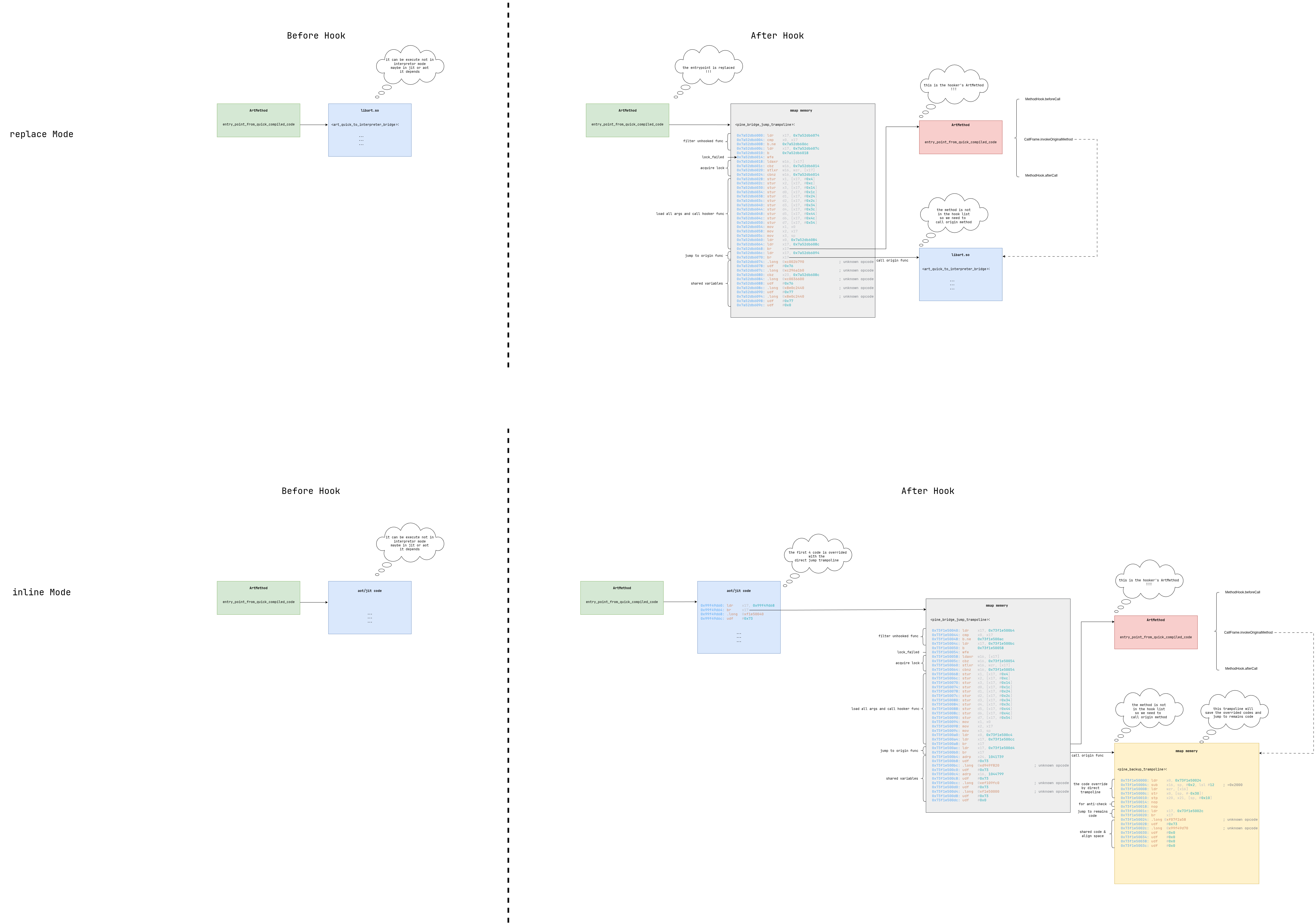

流程图:

参考

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 理想三旬!